LazyGamer

FPS Junkie

- Joined

- Sep 5, 2020

- Messages

- 3,082

- Reaction score

- 2,137

If ASML machines aren't putting out, won't TSMC run up against the same issues?18A isn't what it's been hyped up to be.

If ASML machines aren't putting out, won't TSMC run up against the same issues?18A isn't what it's been hyped up to be.

I think it's not just about the machines. It's more about passionate people wanting to do their best. I don't know what kind of culture Intel fabs have but I have read that at TSMC, almost everyone on the fab floor is a PhD with expertise in some area that helps TSMC be the best. Unlike Intel, they have never rested on their laurels. They take their commitment to their customers more seriously than death itself.If ASML machines aren't putting out, won't TSMC run up against the same issues?

Right now Intel is going to the government trough to sustain itself. And that trough is filled with TAA compliance, and security requirements, and NOT gaming performance... they will sustain themselves and get funding for more production from the US government, even if we have to invade another country for the raw materials... looking at you Iceland/Greenland. (And yea I don't want to get into the politics of it... but it is what it is... disgusting or not.)The problem with the 'desktop' space is that... most of that is ordered by the big three OEMs, and desktop CPUs are basically a commodity. As in, it doesn't even matter which one is 'better', it's which one fits their requirements and they can get the best deal on.

To that end, for corporate desktops, Intel is plenty experienced in 'checking the boxes'.

But for enthusiasts, especially gamers... they've been missing the mark, and I think they know it.

lets see, we could use some seesaw.It's literally just the cache (and/or the resulting frametime consistency).

Intel fixes that, and they're back on top.

They absolutely have the opportunity to drive the market.This is how Intel could potentially un-screw itself:

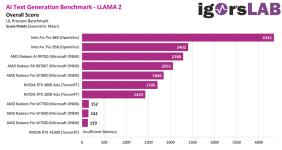

They can sell these to corporations for providing cloud AI services. Eight GPU servers etc. Should be more cost effective than going Nvidia.How big is the market for local large language models?